Auf den aktuellen Märkten herrscht großer Druck auf Elektronikunternehmen, immer mehr miniaturisierte Produkte in immer kürzeren Zeiten und mit immer geringeren Kosten zu entwickeln und zu produzieren. Um die geforderten Qualitätsstandards zu gewährleisten, ist es notwendig, die Anzahl der Designiterationen auf ein Minimum zu reduzieren, wettbewerbsfähig zu bleiben und die Markteinführungsdauer so weit wie möglich zu verkürzen.

Im Hinblick auf das Design einer Leiterplatte gibt es im Wesentlichen zwei grundlegende Anforderungen, die jedes Projekt erfüllen muss:

- Die Leiterplatte muss in großem Maßstab zuverlässig produziert werden.

- Die Leiterplatte muss ohne Probleme bestückt werden können.

Diese Anforderungen sind aufgrund des umfangreichen Komponenteneinsatzes mit ultrakleinen Gehäusen und der zunehmenden Komponentendichte auf der Leiterplatte zunehmend schwieriger zu erfüllen. Entwickler müssen daher geeignete Kontrollen einführen, die während der verschiedenen Schritte des Entwicklungszyklus durchgeführt und wiederholt werden, um sicherzustellen, dass das endgültige Produkt funktioniert und wie beabsichtigt durchführbar ist. Es ist wichtig zu beachten, dass dieser Prozess in der Regel nicht nur die Konstrukteure, sondern auch die Hersteller und Bestücker der Leiterplatte miteinbezieht.

und erhalten Sie innerhalb von 10 Minuten ein Angebot für Ihr PCBA-Projekt

DFM und DFA

Die beiden Konzepte, welche die oben genannten Anforderungen zusammenfassen, sind DFM und DFA.

DFM (Design für Herstellung) stellt sicher, dass das Leiterplattendesign die Anforderungen des Herstellungsprozesses erfüllt – basierend auf Eigenschaften wie der minimalen Leiterbahnbreite, dem minimalen Abstand zwischen Leiterbahnen, der minimalen Bohrungsbreite und mehr – , die überprüft werden müssen, bevor die Leiterplatte in Produktion geht. Es geht daher darum, mögliche Probleme auf Leiterplattenlayoutebene durch eine Reihe von Regeln oder Kontrollen, mit dem Namen DRC (Designregelüberprüfung), vorwegzunehmen.

DFA (Design für Bestückung) hat stattdessen das Ziel, die Auswirkungen zu bewerten, welche die Designentscheidungen auf die Leiterplattenbestückung haben werden. Ziel des DFA ist, ein Produkt mit einer optimalen Anzahl von Komponenten zu erhalten, das Prozesse und Materialien erfordert, welche die Bestückung vereinfachen und die Gesamtkosten senken können.

Daher füllen DFM- und DFA-Analysetechniken die möglichen Lücken zwischen dem Design einer Leiterplatte und deren Produktions- und Bestückungsphasen, basierend auf der Steuerung einiger Parameter und Schlüsselfaktoren, die heute weitgehend durch automatische Werkzeuge durchgeführt werden können. Die Kosten im Zusammenhang mit dem Fehlen oder dem Mangel an DFM- und DFA-Analyse können die Leiterplattenendkosten erheblich beeinflussen (um bis zu 20 %). Daher ist es wichtig, dass die DFM- und DFA-Analyse frühzeitig vor der Vorbereitung der ersten Prototypen durchgeführt wird, um Probleme oder unerwartete Kosten während der Produktions- und Bestückungsschritte zu vermeiden.

Die wichtigsten Vorteile der DFM- und DFA-Analyse lassen sich wie folgt zusammenfassen:

- Reduzierung der für die Produktentwicklung erforderlichen Iterationen

- Reduzierung der Markteinführungsdauer

- Reduzierung des Prozentsatzes der Fehler, die während der Produktions- und Bestückungsschritte festgestellt werden

- Erhöhung der Zuverlässigkeit und Haltbarkeit des Produkts

- Kostensenkung

DFM-Analyse

Jedes PCB-Projekt erzeugt in der Ausgabe einen Satz Gerber-Dateien, die detaillierte Informationen zu folgenden Themen enthalten:

- verwendete Materialien und ihre Eigenschaften

- Stapelungstyp und Eigenschaften jeder einzelnen Ebene

- Anzahl, Position und Eigenschaften der Bohrungen

- Anzahl, Position und Eigenschaften der Testpunkte

- auf die Leiterplatte aufzutragende Oberflächenbehandlung

- Informationen zu Lötmaske und Siebdruck

- Informationen zur Leiterplattenverkleidung

Durch die Durchführung der DFM-Analyse können die Hersteller anhand dieser Informationen beurteilen, ob eine Platine tatsächlich mit den verfügbaren Geräten und Prozessen hergestellt werden kann. Während dieser Phase können potenzielle Probleme erkannt werden, die den Herstellungsprozess ernsthaft beeinträchtigen könnten. So könnte die DFM-Analyse beispielsweise das Vorhandensein von spitzen Winkeln auf den Leiterbahnen aufzeigen, die möglicherweise Säure während des Ätzprozesses der Platte zurückhalten können. Die eingeschlossene Säure könnte Verbindungsprobleme verursachen, in der Regel offene Stromkreise. Uns ist bekannt, dass die Lösung dieses Problems darin besteht, spitze Winkel durch Bögen oder durch ein Paar 45-Grad-Winkel zu ersetzen. Obwohl dies ein sehr einfaches Beispiel ist, gibt es viele andere Probleme, die während der Leiterplatten-Entwicklungsphase nicht leicht zu erkennen sind.

Nachfolgend eine Auswahl der häufigsten Probleme:

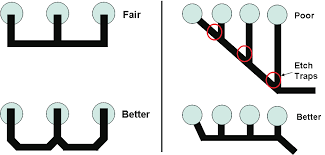

- Säurefallen– wir haben dieses klassische Problem der Leiterplattentopologie bereits vorweggenommen. Dieses Problem betrifft in der Regel alle spitzen Winkel (wie im Beispiel in Abbildung 1), in denen die Säure während der Waschphase zurückbleiben kann, anstatt wie vorgesehen abzufließen. Nach einem konsequenten „Überätzungs“-phänomen (nicht besonders schwierig bei 0,10 oder 0,13 mm dicken Leiterbahnen), könnten einige Leiterbahnen unterbrochen werden

Abbildung 1: Beispiel einer Säurefalle (Quelle: TI)

- Kupfer- oder Lötmaskensplitter – diese Fragmente (leitend im Fall von Kupfer oder nicht leitend im Fall von Lötmasken) können sich auf der Leiterplatte ablagern und mögliche Kurzschlüsse verursachen. Wenn sie groß sind, können sie zu tatsächlichen Antennen werden, was die Bildung von Rauschen oder Interferenzen zur Folge haben kann, insbesondere wenn sie Spuren mit Hochgeschwindigkeitssignalen beeinflussen. Die beste Lösung für dieses Problem besteht darin, das Zurückbleiben zu dünner Kupferflächen zu vermeiden, insbesondere dort, wo Spuren Pads kreuzen. Eine Mindestauflösung des Ätzprozesses von 0,10 bis 0,15 mm vermeidet die

- Problemverbindungen (auch „verhungerte Wärmeströme“ genannt), die von der Leistungsebene isoliert bleiben– diese Verbindungen verbinden die Wärmeleitpads in der Regel mit den thermischen Dispersionsebenen, die erforderlich sind, um die Wärme während des Lötprozesses effektiv abzuleiten. Manchmal kann sich zwischen dem Wärmeleitpad und der Ebene eine Lücke bilden, die eine schlechte Verbindung erzeugt und die Effektivität der Wärmeübertragung minimiert. Verhungerte Wärmeströme können sowohl beim Schweißen als auch während des Bestückungsprozesses zu Problemen führen. Eine falsche Wärmeübertragung kann auch zu Überhitzung und somit zu Schäden an der Platine führen.

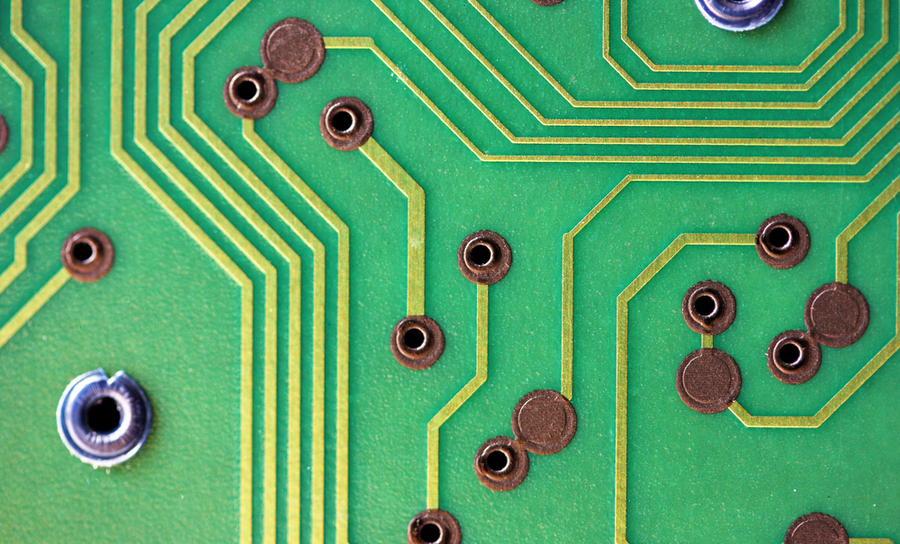

- mangelhaftes Lötauge– wenn die Größe einer Bohrung größer als die des runden Pads ist, auf dem es gebohrt werden soll, kann es zu einer Trennung des Pins oder einem Kurzschluss kommen. Es ist daher notwendig, in der Layoutdefinitionsphase für jedes Lötauge ausreichend Platz zu schaffen (wie in Abbildung 2 gezeigt).

Abbildung 2: Lötauge auf runden Pads (Quelle: Altium)

- Kupfer zu nahe an den Kanten der Platine– auch in diesem Fall muss ein angemessener Abstand zwischen jeder Kupferspur oder ‑ebene und den Kanten der Leiterplatte eingehalten werden. Andernfalls besteht die Möglichkeit, dass Kurzschlüsse oder elektrische Entladungen auftreten, wenn die Platine mit Strom versorgt wird.

- Fehlende oder mangelhafte Lötmaske– auch wenn die Lötmaske nicht unbedingt in allen Anwendungen erforderlich ist, bietet sie den Vorteil, den Stromkreis vor Oxidations- und atmosphärischen Substanzen zu schützen, die Lötphase zu vereinfachen und zuverlässiger zu machen.

- Verwendung ungeeigneter Materialien und Substrate– elektronische Geräte der neuesten Generation nutzen digitale Signale und Taktquellen mit immer höheren Frequenzen, die immer näher an den Hochfrequenzbereich heranrücken. In vielen Fällen kann sich ein herkömmliches Substrat wie FR-4 (billig und leicht erhältlich) als unzureichend erweisen, was zu gefährlicher Überhitzung, thermischer Drift oder sogar zu Schäden an der Platine führen kann. Die für die Substrate verwendeten Materialien, eventuell miteinander kombiniert, müssen vor der Produktion der Leiterplatte entsprechend ausgewählt werden.

Obwohl es zahlreiche mögliche Fehler gibt, die der Designer bei der Definition des Layouts machen kann, ermöglicht die Durchführung der DFM-Analyse deren Identifizierung in den frühen Entwicklungsphasen. Heute sind mehrere DFM-Tools auf dem Markt erhältlich, die den Designer in dieser heiklen Phase unterstützen und so hohe Neuplanungskosten zu vermeiden. Solche Werkzeuge können von Designern verwendet werden, die nicht unbedingt gut in der Herstellung sind. Darüber hinaus ist es möglich, vordefinierte Parameter und Regeln für jeden Hersteller zu konfigurieren und so die DFM-Analyse an die tatsächlichen Eigenschaften und Systeme derjenigen anzupassen, die sich tatsächlich mit der Produktion befassen müssen.

DFA-Analyse

Die Bestückung kann als der zeitaufwendigste und kostenintensivste Herstellungsprozess für Leiterplatten angesehen werden. Die Design- und Entwicklungsphasen einer Leiterplatte umfassen zwei Bestückungsphasen: die Bestückung der Prototypplatine und die Bestückung der Produktionsplatine. Beide Phasen sollten bei der Entwicklung der Leiterplatte in die DFA-Analyse einbezogen werden.

Obwohl sich das Ziel der DFA-Analyse von dem der DFM-Analyse unterscheidet, sind viele Techniken und Strategien austauschbar auf alle Phasen des Leiterplattendesigns anwendbar. Die DFA-Analyse konzentriert sich auf die Bestückungsphase und berücksichtigt zunächst die Besonderheiten und Eigenschaften der Komponenten, die auf der Leiterplatte montiert werden, mit dem Ziel, deren Anzahl und Typen zu minimieren, wobei Standardkomponenten bevorzugt werden, die zuverlässig, leicht zu finden und einfach bestückbar sind.

Die DFA-Analyse führt in der Regel zu einer Verbesserung der Leiterplattenzuverlässigkeit, indem beispielsweise nur Komponenten von Herstellern ausgewählt werden, die eine zuverlässige Genauigkeit, Stabilität und Liefertreue garantieren. Wenn beispielsweise die DFA-Analyse zeigt, dass eine bestimmte Komponente veraltet ist, sollte der Designer Informationen über einen möglichen geeigneten Ersatz bereitstellen.

Obwohl die während der DFA-Analyse durchgeführten Kontrollen breit gefächert und zahlreich sind, kann eine mögliche Auswahl wie folgt getroffen werden:

- Übereinstimmung zwischen den einzelnen Komponenten und den relativen Pads

- Mindestabstand zwischen den Komponenten

- korrektes Vorhandensein von Lötmaske und Passermarkern

- korrekte Größe und Position der Bohrungen

- Verfügbarkeit von ausreichend freiem Platz an den Kanten der Platte

- Angemessene Anwendung von thermischen Entlastungen

- Verfügbarkeit von Komponenten, aktuell und mittel- bis langfristig

- Möglichkeit der Panelisierung der Platte für die Großproduktion

- Testbarkeit der Platte

- Beständigkeit gegen Vibrationen und mechanische Beanspruchungen, je nach Anwendung

Wenn Designer die Anwendung der DFA-Technik als wesentlichen Bestandteil des Leiterplattendesigns vernachlässigen, ist es viel wahrscheinlicher, dass es bei der Bestückung der Platine zukünftigen Problemen kommt, was zu einer Verlängerung des Produktionszyklus und höheren Kosten führt.

Der Einsatz von DFA-Analysen garantiert nicht nur einen optimalen Betrieb des Stromkreises, sondern stellt auch sicher, dass er in großem Maßstab hergestellt und montiert werden kann, ohne Kosten, Risiken und Zeit zu erhöhen.

04.01.2022